Bab 6. I/O dan Disk

Perangkat Keras I/O

Secara umum, terdapat beberapa jenis seperti device penyimpanan (disk, tape), transmission device (network card, modem), dan human-interface device (screen, keyboard, mouse). Device tersebut dikendalikan oleh instruksi I/O. Alamat-alamat yang dimiliki oleh device akan digunakan oleh direct I/O instruction dan memory-mapped I/O.

Beberapa konsep yang umum digunakan ialah port, bus (daisy chain/ shared direct access), dan controller (host adapter). Port adalah koneksi yang digunakan oleh device untuk berkomunikasi dengan mesin. Bus adalah koneksi yang menghubungkan beberapa device menggunakan kabel-kabel. Controller adalah alat-alat elektronik yang berfungsi untuk mengoperasikan port, bus, dan device.

Langkah yang ditentukan untuk device adalah command-ready, busy, dan error. Host mengeset command-ready ketika perintah telah siap untuk dieksekusi oleh controller. Controller mengeset busy ketika sedang mengerjakan sesuatu, dan men clear busy ketika telah siap untuk menerima perintah selanjutnya. Error diset ketika terjadi kesalahan.

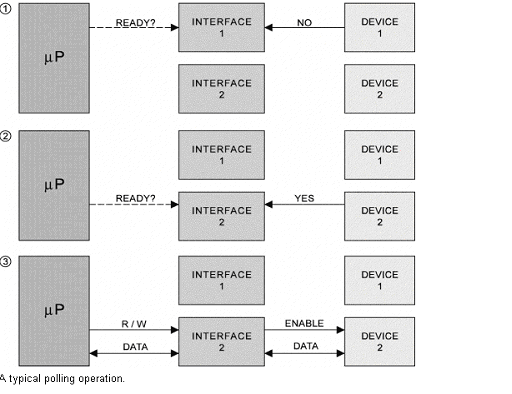

Polling

Busy-waiting/ polling adalah ketika host mengalami looping yaitu membaca status register secara terus-menerus sampai status busy di-clear. Pada dasarnya polling dapat dikatakan efisien. Akan tetapi polling menjadi tidak efisien ketika setelah berulang-ulang melakukan looping, hanya menemukan sedikit device yang siap untuk men-service, karena CPU processing yang tersisa belum selesai.

Interupsi

Mekanisme Dasar Interupsi

Ketika CPU mendeteksi bahwa sebuah controller telah mengirimkan sebuah sinyal ke interrupt request line (membangkitkan sebuah interupsi), CPU kemudian menjawab interupsi tersebut (juga disebut menangkap interupsi) dengan menyimpan beberapa informasi mengenai state terkini CPU--contohnya nilai instruksi pointer, dan memanggil interrupt handler agar handler tersebut dapat melayani controller atau alat yang mengirim interupsi tersebut.

Fitur Tambahan pada Komputer Modern

Pada arsitektur komputer modern, tiga fitur disediakan oleh CPU dan interrupt controller (pada perangkat keras) untuk dapat menangani interrupsi dengan lebih bagus. Fitur-fitur ini antara lain adalah kemampuan menghambat sebuah proses interrupt handling selama prosesi berada dalam critical state, efisiensi penanganan interupsi sehingga tidak perlu dilakukan polling untuk mencari device yang mengirimkan interupsi, dan fitur yang ketiga adalah adanya sebuah konsep multilevel interupsi sedemikian rupa sehingga terdapat prioritas dalam penanganan interupsi (diimplementasikan dengan interrupt priority level system).

Interrupt Request Line

Pada peranti keras CPU terdapat kabel yang disebut interrupt request line, kebanyakan CPU memiliki dua macam interrupt request line, yaitu nonmaskable interrupt dan maskable interrupt. Maskable interrupt dapat dimatikan/ dihentikan oleh CPU sebelum pengeksekusian deretan critical instruction (critical instruction sequence) yang tidak boleh diinterupsi. Biasanya, interrupt jenis ini digunakan oleh device controller untuk meminta pelayanan CPU.

Interrupt Vector dan Interrupt Chaining

Sebuah mekanisme interupsi akan menerima alamat interrupt handling routine yang spesifik dari sebuah set, pada kebanyakan arsitektur komputer yang ada sekarang ini, alamat ini biasanya berupa sekumpulan bilangan yang menyatakan offset pada sebuah tabel (biasa disebut interrupt vector). Tabel ini menyimpan alamat-alamat interrupt handler spesifik di dalam memori. Keuntungan dari pemakaian vektor adalah untuk mengurangi kebutuhan akan sebuah interrupt handler yang harus mencari semua kemungkinan sumber interupsi untuk menemukan pengirim interupsi.

Akan tetapi, interrupt vector memiliki hambatan karena pada kenyataannya, komputer yang ada memiliki device (dan interrupt handler) yang lebih banyak dibandingkan dengan jumlah alamat pada interrupt vector. Karena itulah, digunakanlah teknik interrupt chaining dimana setiap elemen dari interrupt vector menunjuk/ merujuk pada elemen pertama dari sebuah daftar interrupt handler. Dengan teknik ini, overhead yang dihasilkan oleh besarnya ukuran tabel dan inefisiensi dari penggunaan sebuah interrupt handler (fitur pada CPU yang telah disebutkan sebelumnya) dapat dikurangi, sehingga keduanya menjadi kurang lebih seimbang.

Penyebab Interupsi

Interupsi dapat disebabkan berbagai hal, antara lain exception, page fault, interupsi yang dikirimkan oleh device controllers, dan system call Exception adalah suatu kondisi dimana terjadi sesuatu/ dari sebuah operasi didapat hasil tertentu yang dianggap khusus sehingga harus mendapat perhatian lebih, contoh nya pembagian dengan 0 (nol), pengaksesan alamat memori yang restricted atau bahkan tidak valid, dan lain-lain. System call adalah sebuah fungsi pada aplikasi (perangkat lunak) yang dapat mengeksekusikan instruksi khusus berupa software interrupt atau trap.

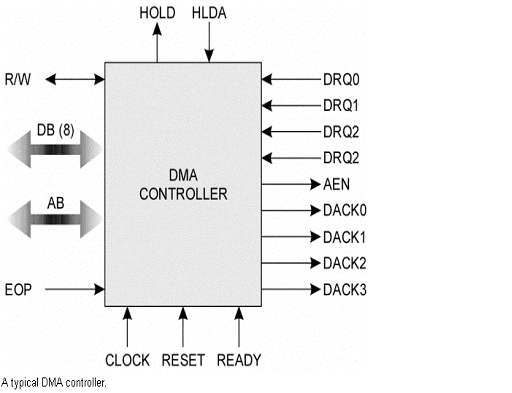

DMA

Definisi

DMA adalah sebuah prosesor khusus (special purpose processor) yang berguna untuk menghindari pembebanan CPU utama oleh program I/O (PIO).

Transfer DMA

Untuk memulai sebuah transfer DMA, host akan menuliskan sebuah DMA command block yang berisi pointer yang menunjuk ke sumber transfer, pointer yang menunjuk ke tujuan/ destinasi transfer, dan jumlah byte yang ditransfer, ke memori. CPU kemudian menuliskan alamat command block ini ke DMA controller, sehingga DMA controller dapat kemudian mengoperasikan bus memori secara langsung dengan menempatkan alamat-alamat pada bus tersebut untuk melakukan transfer tanpa bantuan CPU. Tiga langkah dalam transfer DMA:

Prosesor menyiapkan DMA transfer dengan menyedia kan data-data dari device, operasi yang akan ditampilkan, alamat memori yang menjadi sumber dan tujuan data, dan banyaknya byte yang di transfer.

DMA controller memulai operasi (menyiapkan bus, menyediakan alamat, menulis dan membaca data), sampai seluruh blok sudah di transfer.

DMA controller meng-interupsi prosesor, dimana selanjutnya akan ditentukan tindakan berikutnya.

Pada dasarnya, DMA mempunyai dua metode yang berbeda dalam mentransfer data. Metode yang pertama adalah metode yang sangat baku dan simple disebut HALT, atau Burst Mode DMA, karena DMA controller memegang kontrol dari sistem bus dan mentransfer semua blok data ke atau dari memori pada single burst. Selagi transfer masih dalam progres, sistem mikroprosessor di-set idle, tidak melakukan instruksi operasi untuk menjaga internal register. Tipe operasi DMA seperti ini ada pada kebanyakan komputer.

Metode yang kedua, mengikut-sertakan DMA controller untuk memegang kontrol dari sistem bus untuk jangka waktu yang lebih pendek pada periode dimana mikroprosessor sibuk dengan operasi internal dan tidak membutuhkan akses ke sistem bus. Metode DMA ini disebut cycle stealing mode. Cycle stealing DMA lebih kompleks untuk diimplementasikan dibandingkan HALT DMA, karena DMA controller harus mempunyai kepintaran untuk merasakan waktu pada saat sistem bus terbuka.

Handshaking

Proses handshaking antara DMA controller dan device controller dilakukan melalui sepasang kabel yang disebut DMA-request dan DMA-acknowledge. Device controller mengirimkan sinyal melalui DMA-request ketika akan mentransfer data sebanyak satu word. Hal ini kemudian akan mengakibatkan DMA controller memasukkan alamat-alamat yang dinginkan ke kabel alamat memori, dan mengirimkan sinyal melalui kabel DMA-acknowledge. Setelah sinyal melalui kabel DMA-acknowledge diterima, device controller mengirimkan data yang dimaksud dan mematikan sinyal pada DMA-request.

Hal ini berlangsung berulang-ulang sehingga disebut handshaking. Pada saat DMA controller mengambil alih memori, CPU sementara tidak dapat mengakses memori (dihalangi), walau pun masih dapat mengaksees data pada cache primer dan sekunder. Hal ini disebut cycle stealing, yang walau pun memperlambat komputasi CPU, tidak menurunkan kinerja karena memindahkan pekerjaan data transfer ke DMA controller meningkatkan performa sistem secara keseluruhan.

Cara-cara Implementasi DMA

Dalam pelaksanaannya, beberapa komputer menggunakan memori fisik untuk proses DMA , sedangkan jenis komputer lain menggunakan alamat virtual dengan melalui tahap "penerjemahan" dari alamat memori virtual menjadi alamat memori fisik, hal ini disebut direct virtual-memory address atau DVMA. Keuntungan dari DVMA adalah dapat mendukung transfer antara dua memory mapped device tanpa intervensi CPU.